Data Sheet

## July 31, 2006

# Four-Channel Programmable Digital DownConverter

intercil

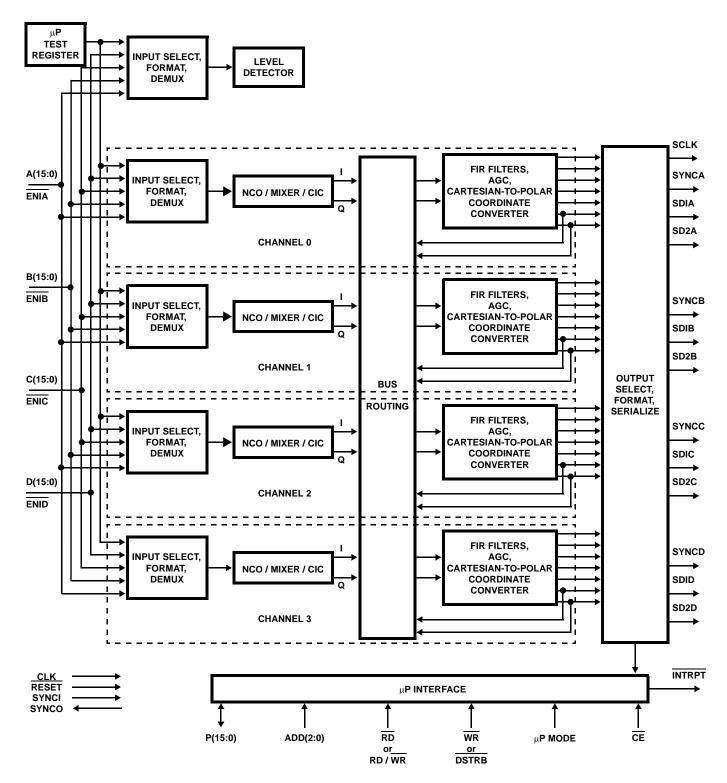

The HSP50216 Quad Programmable Digital DownConverter (QPDC) is designed for high dynamic range applications such as cellular basestations where multiple channel processing is required in a small physical space. The QPDC combines into a single package, a set of four channels which include: digital mixers, a quadrature carrier NCO, digital filters, a resampling filter, a Cartesian-to-polar coordinate converter and an AGC loop.

The HSP50216 accepts four channels of 16-bit real digitized IF samples which are mixed with local quadrature sinusoids. Each channel carrier NCO frequency is set independently by the microprocessor. The output of the mixers are filtered with a CIC and FIR filters, with a variety of decimation options. Gain adjustment is provided on the filtered signal. The digital AGC provides a gain adjust range of up to 96dB with programmable thresholds and slew rates. A cartesian to polar coordinate converter provides magnitude and phase outputs. A frequency discriminator provides a frequency output via the FIR filter. Selectable outputs include I samples, Q samples, Magnitude, Phase, Frequency and AGC gain. The output resolution is selectable from 4-bit fixed point to 32-bit floating point.

The maximum output bandwidth achievable using a single channel is at least 1MHz.

# Ordering Information

| PART<br>NUMBER        | PART<br>MARKING | TEMP<br>RANGE<br>(°C) | PACKAGE                 | PKG. NO    |

|-----------------------|-----------------|-----------------------|-------------------------|------------|

| HSP50216KI            | HSP50216KI      | -40 to 85             | 196 Ld BGA              | V196.12x12 |

| HSP50216KIZ<br>(Note) | HSP50216KIZ     | -40 to 85             | 196 Ld BGA<br>(Pb-free) | V196.12x12 |

NOTE: Intersil Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

# Features

- · Up to 70MSPS Input

- Four Independently Programmable Downconverter Channels in a single package

- Four Parallel 16-Bit Inputs Fixed or Floating Point Format

- 32-Bit Programmable Carrier NCO with > 115dB SFDR

- 110dB FIR Out of Band Attenuation

- Decimation from 8 to >65536

- 24-bit Internal Data Path

- Digital AGC with up to 96dB of Gain Range

- Filter Functions

- 1 to 5 Stage CIC Filter

- Halfband Decimation and Interpolation FIR Filter

- Programmable FIR Filter

- Resampling FIR Filter

- · Cascadable Filtering for Additional Bandwidth

- Four Independent Serial Outputs

- 3.3V Operation

- Pb-Free Plus Anneal Available (RoHS Compliant)

# Applications

- Narrow-Band TDMA through IS-95 CDMA Digital Software Radio and Basestation Receivers

- Wide-Band Applications: W-CDMA and UMTS Digital Software Radio and Basestation Receivers

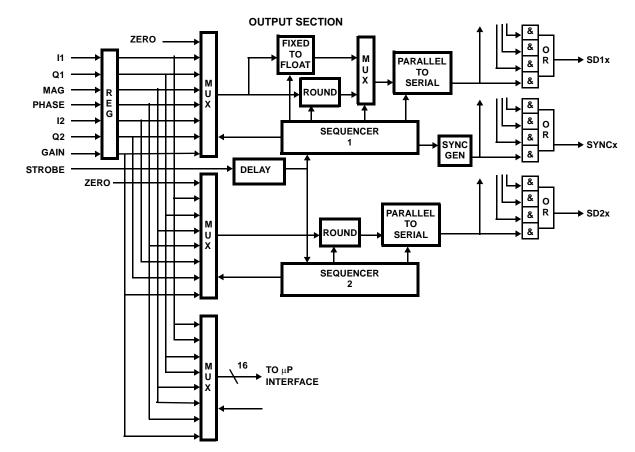

Block Diagram

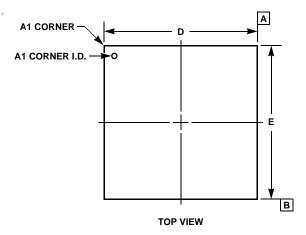

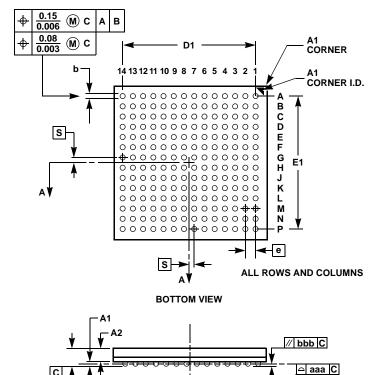

196 LEAD BGA TOP VIEW

|   | 1        | 2              | 3              | 4                        | 5          | 6               | 7                | 8                | 9                | 10              | 11                | 12                  | 13               | 14               |

|---|----------|----------------|----------------|--------------------------|------------|-----------------|------------------|------------------|------------------|-----------------|-------------------|---------------------|------------------|------------------|

| Α | O<br>A5  | O<br>A7        | ()<br>A9       | O<br>A11                 | O<br>A13   | O<br>A15        | O<br>SD1A        | O<br>synca       | О<br>syncb       | O<br>sclk       | O<br>syncc        | O<br>syncd          | O<br>synci       | O<br>synco       |

| в | ()<br>A3 | 0              | 0              | 0                        | 0          |                 | 0                |                  | 0                | ٠               | 0                 | 0                   | 0                | 0                |

| с |          | A6<br>()<br>A2 | A8<br>()<br>A4 | A10<br><u> O</u><br>ENIA |            | GND<br>O<br>A14 | VCC<br>O<br>SD2A | GND<br>O<br>SD1B | VCC<br>O<br>SD2B |                 | SD1C<br>O<br>SD2D | SD1D<br>O<br>INTRPT | ADD0<br>O<br>P15 | ADD1<br>O<br>P14 |

| D | O<br>B15 | O<br>A0        | О<br>в14       | $\otimes$                | $\otimes$  | $\otimes$       | $\otimes$        | $\otimes$        | $\otimes$        | $\otimes$       |                   |                     | O<br>P13         | O<br>P12         |

| E | О<br>в13 | GND            | O<br>B12       | $\otimes$                | 0          | 0               | 0                | 0                | 0                | 0               | $\otimes$         | O<br>P11            | O<br>vcc         | O<br>P10         |

| F | O<br>B11 | O<br>vcc       | О<br>в10       | $\otimes$                | 0          | 0               | igodot           | 0                | 0                | 0               | $\otimes$         | O<br>P9             | <b>GND</b>       | O<br>P8          |

| G | О<br>в9  | <b>GND</b>     | GND            | $\otimes$                | 0          | 0               | 0                | 0                | 0                | 0               | $\otimes$         | О<br>Р7             | O<br>vcc         | O<br>P6          |

| н | О<br>clk | O<br>vcc       | О<br>в8        | $\otimes$                | $\circ$    | 0               | 0                | 0                | 0                | 0               | $\otimes$         | O<br>P5             | GND              | O<br>P4          |

| J | О<br>в7  | <b>GND</b>     | О<br>В6        | $\otimes$                | 0          | 0               | 0                | 0                | 0                | 0               | $\otimes$         | О<br>Р3             | O<br>vcc         | O<br>P2          |

| к | О<br>в5  | O<br>vcc       | О<br>в4        | $\otimes$                | 0          | 0               | 0                | 0                | 0                | 0               |                   | O<br>E P1           | <b>GND</b>       | O<br>P0          |

| L | О<br>вз  | О<br>в2        |                | $\otimes$                | $\otimes$  | $\otimes$       | $\otimes$        | $\otimes$        | $\otimes$        | $\otimes$       | $\otimes$         |                     | $\frac{O}{RD}$   |                  |

| м | О<br>в1  | О<br>во        | O<br>C12       | ()<br>C6                 | O<br>C4    | O<br>C2         | O<br>co          | O<br>D15         | O<br>D13         | O<br>D11        |                   | O<br>D3             | O<br>D1          | O<br>D0          |

| N | O<br>C15 | O<br>C14       | O<br>C10       | O<br>C8                  | <b>GND</b> | O<br>vcc        | GND              | O<br>vcc         | GND              | <b>O</b><br>vcc | O<br>D9           | O<br>d7             | O<br>D5          | O<br>D2          |

| Ρ | O<br>C13 | O<br>C11       | ()<br>C9       | O<br>c7                  | O<br>C5    | О<br>С3         | O<br>C1          |                  | O<br>D14         | O<br>D12        | O<br>D10          | O<br>D8             | O<br>D6          | O<br>D4          |

|   |          |                |                |                          |            |                 |                  |                  |                  |                 |                   |                     |                  |                  |

O POWER PIN

GROUND PIN

SIGNAL PINTHERMAL BALL

⊗ NC (NO CONNECTION)

# **Pin Descriptions**

| NAME         | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                     |

|--------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER SUPPLY |      |                                                                                                                                                                                                                                                                                                                                                                                 |

| VCC          | -    | Positive Power Supply Voltage, 3.3V ±0.15                                                                                                                                                                                                                                                                                                                                       |

| GND          | -    | Ground, 0V.                                                                                                                                                                                                                                                                                                                                                                     |

| INPUTS       |      |                                                                                                                                                                                                                                                                                                                                                                                 |

| A(15:0)      | I    | Parallel Data Input bus A. Sampled on the rising edge of clock when ENIA is active (low).                                                                                                                                                                                                                                                                                       |

| B(15:0)      | I    | Parallel Data Input bus B. Sampled on the rising edge of clock when ENIB is active (low).                                                                                                                                                                                                                                                                                       |

| C(15:0)      | I    | Parallel Data Input bus C. Sampled on the rising edge of clock when ENIC is active (low).                                                                                                                                                                                                                                                                                       |

| D15          | Į    | Parallel Data Input D15 or tuner channel A COF.                                                                                                                                                                                                                                                                                                                                 |

| D14          | Į    | Parallel Data Input D14 or tuner channel A COFSync.                                                                                                                                                                                                                                                                                                                             |

| D13          | I    | Parallel Data Input D13 or tuner channel A SOF.                                                                                                                                                                                                                                                                                                                                 |

| D12          | I    | Parallel Data Input D12 or tuner channel A SOFSync.                                                                                                                                                                                                                                                                                                                             |

| D11          | I    | Parallel Data Input D11 or tuner channel B COF.                                                                                                                                                                                                                                                                                                                                 |

| D10          | Į    | Parallel Data Input D10 or tuner channel B COFSync.                                                                                                                                                                                                                                                                                                                             |

| D9           | I    | Parallel Data Input D9 or tuner channel B SOF.                                                                                                                                                                                                                                                                                                                                  |

| D8           | I    | Parallel Data Input D8 or tuner channel B SOFSync.                                                                                                                                                                                                                                                                                                                              |

| D7           | I    | Parallel Data Input D7 or tuner channel C COF.                                                                                                                                                                                                                                                                                                                                  |

| D6           | I    | Parallel Data Input D6 or tuner channel C COFSync.                                                                                                                                                                                                                                                                                                                              |

| D5           | I    | Parallel Data Input D5 or tuner channel C SOF.                                                                                                                                                                                                                                                                                                                                  |

| D4           | I    | Parallel Data Input D4 or tuner channel C SOFSync.                                                                                                                                                                                                                                                                                                                              |

| D3           | I    | Parallel Data Input D3 or tuner channel D COF.                                                                                                                                                                                                                                                                                                                                  |

| D2           | I    | Parallel Data Input D2 or tuner channel D COFSync.                                                                                                                                                                                                                                                                                                                              |

| D1           | I    | Parallel Data Input D1 or tuner channel D SOF.                                                                                                                                                                                                                                                                                                                                  |

| D0           | I    | Parallel Data Input D0 or tuner channel D SOFSync.                                                                                                                                                                                                                                                                                                                              |

| ENIA         | Ι    | Input enable for Parallel Data Input bus A. Active low. This pin enables the input to the part in one of two modes, gated or interpolated. In gated mode, one sample is taken per CLK when ENI is asserted.                                                                                                                                                                     |

| ENIB         | I    | Input enable for Parallel Data Input bus B. Active low. This pin enables the input to the part in one of two modes, gated or interpolated. In gated mode, one sample is taken per CLK when $\overline{\text{ENI}}$ is asserted.                                                                                                                                                 |

| ENIC         | I    | Input enable for Parallel Data Input bus C. Active low. This pin enables the input to the part in one of two modes, gated or interpolated. In gated mode, one sample is taken per CLK when ENI is asserted.                                                                                                                                                                     |

| ENID         | I    | Input enable for Parallel Data Input bus D. Active low. This pin enables the input to the part in one of two modes, gated or interpolated. In gated mode, one sample is taken per CLK when ENI is asserted.                                                                                                                                                                     |

| CONTROL      |      |                                                                                                                                                                                                                                                                                                                                                                                 |

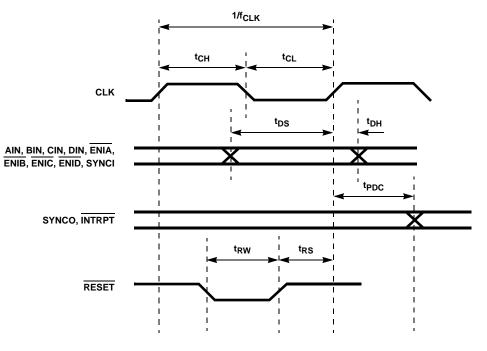

| CLK          | Į    | Input clock. All processing in the HSP50216 occurs on the rising edge of CLK.                                                                                                                                                                                                                                                                                                   |

| SYNCI        | I    | Synchronization Input Signal. Used to align the processing with an external event or with other HSP50216 devices. SYNCI can update the carrier NCO, reset decimation counters, restart the filter compute engine and restart the output section among other functions. For most of the functional blocks, the response to SYNCI is programmable and can be enabled or disabled. |

| SYNCO        | 0    | Synchronization Output Signal. The processing of multiple HSP50216 devices can be synchronized by tying the SYNCO from one HSP50216 device (the master) to the SYNCI of all the HSP50216 devices (the master and slaves).                                                                                                                                                       |

| RESET        | I    | Reset Signal. Active low. Asserting reset will halt all processing and set certain registers to default values.                                                                                                                                                                                                                                                                 |

# Pin Descriptions (Continued)

| NAME              | TYPE          | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DUTPUTS           |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SD1A              | 0             | Serial Data Output 1A. A serial data stream output which can be programmed to consist of I1, Q1, I2, Q2, magnitude, phase, frequency (d\u00f6/dt), AGC gain, and/or zeros. In addition, data outputs from Channels 0, 1, 2 and 3 can be multiplexed into a common serial output data stream. Information can be sequenced in a programmable order. See Serial Data Output Formatter Section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SD2A              | 0             | Serial Data Output 2A. This output is provided as an auxiliary output for Serial Data Output 1A to route data to a second destination or to output two words at a time for higher sample rates. SD2A has the same programmability as SD1A except that floating point format is not available. See Serial Data Output Formatter Section and Microprocessor Interface section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SD1B              | 0             | Serial Data Output 1B. See description for SD1A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SD2B              | 0             | Serial Data Output 2B. See description for SD2A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SD1C              | 0             | Serial Data Output 1C. See description for SD1A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SD2C              | 0             | Serial Data Output 2C. See description for SD2A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SD1D              | 0             | Serial Data Output 1D. See description for SD1A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SD2D              | 0             | Serial Data Output 2D. See description for SD2A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SCLK              | 0             | Serial Output Clock. Can be programmed to be at 1, 1/2, 1/4, 1/8, or 1/16 times the clock frequency. The polarity of SCLK is programmable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SYNCA             | 0             | Serial Data Output 1A sync signal. This signal is used to indicate the start of a data word and/or frame of data. The polarity and position of SYNCA is programmable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SYNCB             | 0             | Serial Data Output 1B sync signal. This signal is used to indicate the start of a data word and/or frame of data. The polarity and position of SYNCB is programmable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SYNCC             | 0             | Serial Data Output 1C sync signal. This signal is used to indicate the start of a data word and/or frame of data. The polarity and position of SYNCC is programmable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SYNCD             | 0             | Serial Data Output 1D sync signal. This signal is used to indicate the start of a data word and/or frame of data. The polarity and position of SYNCD is programmable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| IICROPROCES       | SOR INTERFACE |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

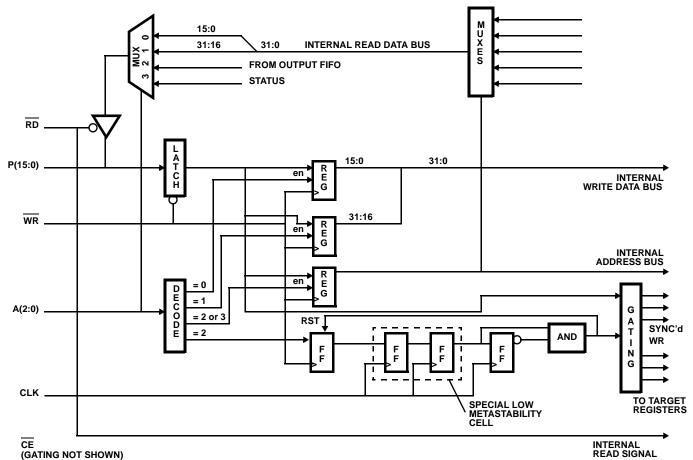

| P(15:0)           | I/O           | Microprocessor Interface Data bus. See "Microprocessor Interface" on page 29. P15 is the MSB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ADD(2:0)          | I             | Microprocessor Interface Address bus. ADD2 is the MSB. See <i>"Microprocessor Interface"</i> on page 29. Note: ADD2 <b>is not</b> used but designated for future expansion.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| WR<br>or<br>DSTRB | 1             | Microprocessor Interface Write or Data Strobe Signal. When the Microprocessor Interface Mode Control, $\mu$ P MODE, is a low data transfers (from either P(15:0) to the internal write holding register or from the internal write holding register to the target register specified) occur on the low to high transition of $\overline{WR}$ when $\overline{CE}$ is asserted (low). When the $\mu$ P MODE control is high this input functions as a data read/write strobe. In this mode with RD/WR low data transfers (from either P(15:0) to the internal write holding register or from the internal write holding register to the target register specified) occur on the low to high transition of Data Strobe. With RD/WR high the data from the address specified is placed on P(15:0) when Data Strobe is low. See <i>"Microprocessor Interface"</i> on page 29. |

| RD<br>or<br>RD/WR | 1             | Microprocessor Interface Read or Read/Write Signal. When the Microprocessor Interface Mode Control, $\mu$ P MODE, is a low the data from the address specified is placed on P(15:0) when RD is asserted (low) and CE is asserted (low). When the $\mu$ P MODE control is high this input functions as a Read/Write control input. Data is read from P(15:0) when high or written to the appropriate register when low. See <i>"Microprocessor Interface" on page 29.</i>                                                                                                                                                                                                                                                                                                                                                                                                  |

| $\mu P MODE$      | I             | Microprocessor Interface Mode Control. This pin is used to select the Read/Write mode for the Microprocessor Interface. Internally pulled down. See "Microprocessor Interface" on page 29.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CE                | I             | Microprocessor Interface Chip Select. Active low. This pin has the same timing as the address pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| INTRPT            | 0             | Microprocessor Interrupt Signal. Asserted for a programmable number of clock cycles when new data is available on the selected Channel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

# Functional Description

The HSP50216 is a four channel digital receiver integrated circuit offering exceptional dynamic range and flexibility. Each of the four channels consists of a front-end NCO, digital mixer, and CIC-filter block and a back-end FIR, AGC and Cartesian to polar coordinate-conversion block. The parameters for the four channels are independently programmable. Four parallel data input busses (A(15:0), B(15:0), C(15:0) and D(15:0)) and four pairs of serial data outputs (SDxA, SDxB, SDxC, and SDxD; x = 1 or 2) are provided. Each input can be connected to any or all of the internal signal processing channels, Channels 0, 1, 2 and 3. The output of each channel can be routed to any of the serial outputs. Outputs from more than one channel can be multiplexed through a common output if the channels are synchronized. The four channels share a common input clock and a common serial output clock, but the output sample rates can be synchronous or asynchronous. Bus multiplexers between the front end and back end sections provide flexible routing between channels for cascading back-end filters or for routing one front end to multiple back ends for polyphase filtering or systolic arrays (to provide wider bandwidth filtering). A level detector is provided to monitor the signal level on any of the parallel data input busses, facilitating microprocessor control of gain blocks prior to an A/D converter.

Each front end NCO/digital mixer/CIC filter section includes a quadrature numerically controlled oscillator (NCO), digital mixer, barrel shifter and a cascaded-integrator-comb filter (CIC). The NCO has a 32-bit frequency control word for 16.3mHz tuning resolution at an input sample rate of 70MSPS. The SFDR of the NCO is >115dB. The barrel shifter provides a gain of between 2<sup>-45</sup> and 2<sup>-14</sup> to prevent overflow in the CIC. The CIC filter order is programmable between 1 and 5 and the CIC decimation factor can be programmed from 4 to 512 for 5<sup>th</sup> order, 2048 for 4<sup>th</sup> order, 32768 for 3<sup>rd</sup> order, or 65536 for 1<sup>st</sup> or 2<sup>nd</sup> order filters.

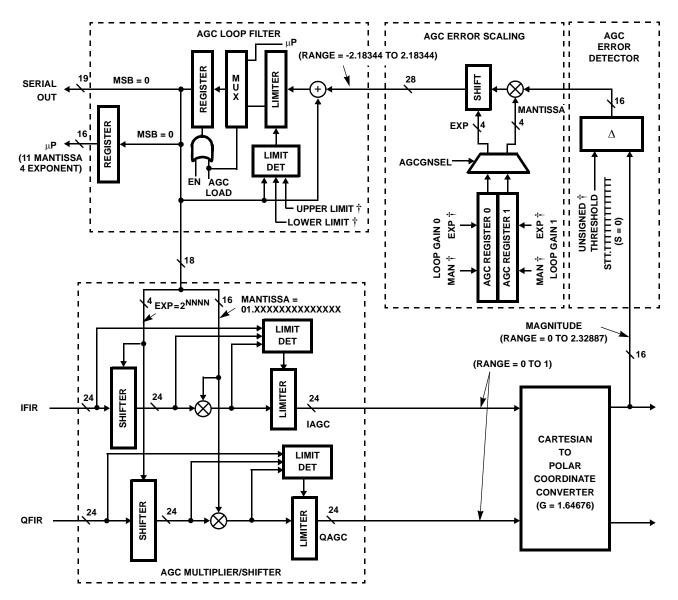

Each channel back end section includes an FIR processing block, an AGC and a cartesian-to-polar coordinate converter. The FIR processing block is a flexible filter compute engine that can compute a single FIR or a set of cascaded decimating filters. A single filter in a chain can have up to 256 taps and the total number of taps in a set of filters can be up to 384 provided that the decimation is sufficient. The HSP50216 calculates 2 taps per clock (on each channel) for symmetric filters, generally making decimation the limiting factor for the number of taps available. The filter compute engine supports a variety of filter types including decimation, interpolation and resampling filters. The coefficients for the programmable digital filters are 22 bits wide. Coefficients are provided in ROM for several halfband filter responses and for a resampler. The AGC section can provide up to 96dB of either fixed or automatic gain control. For automatic gain control, two settling modes and two sets of loop gains are provided. Separate attack and decay slew rates are provided for each loop gain. Programmable limits allow the user to select a gain range less than 96dB. The outputs of the cartesian-to-polar coordinate conversion block, used by the AGC loop, are also provided as outputs to the user for AM and FM demodulation.

The HSP50216 supports both fixed and floating point parallel data input modes. The floating point modes support gain ranging A/D converters. Gated, interpolated and multiplexed data input modes are supported. The serial data output word width for each data type can be programmed to one of ten output bit widths from 4-bit fixed point through 32bit IEEE 754 floating point.

The HSP50216 is programmed through a 16-bit microprocessor interface. The output data can also be read via the microprocessor interface for all channels that are synchronized. The HSP50216 is specified to operate to a maximum clock rate of 70MSPS over the industrial temperature range (-40°C to 85°C). The power supply voltage range is  $3.3V \pm 0.15V$ . The I/Os **are not** 5V tolerant.

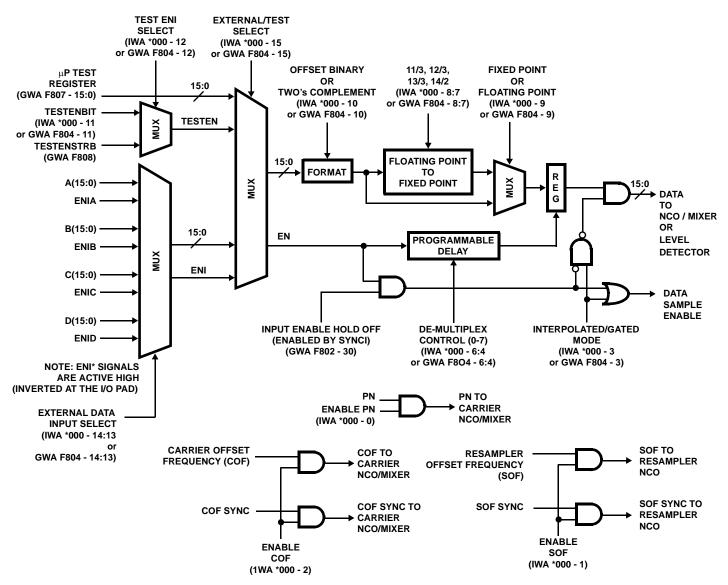

# Input Select/Format Block

Each front end block and the level detector block contains an input select/format block. A functional block diagram is provided in the above figure. The input source can be any of the four parallel input busses (See *Microprocessor Interface* section, Table 3, "CHANNEL INPUT SELECT/FORMAT REGISTER (IWA = \*000h)," on page 32 or a test register loaded via the processor bus (see *Microprocessor Interface* section, Table 42, "mP/TEST INPUT BUS REGISTER (GWA = F807h)," on page 45).

The input to the part can operate in a gated or interpolated mode. Each input channel has an input enable ( $\overline{ENIx}$ , x = A, B, C or D). In the gated mode, one input sample is processed per clock that the  $\overline{ENIx}$  signal is asserted (low). Processing is disabled when  $\overline{ENIx}$  is high. The  $\overline{ENIx}$  signal is pipelined through the part to minimize delay (latency). In the interpolated mode, the input is zeroed when the  $\overline{ENIx}$  signal is high, but processing inside the part continues. This mode

inserts zeros between the data samples, interpolating the input data stream up to the clock rate. On reset, the part is set to gated mode and the input enables are disabled. The inputs are enabled by the first SYNCI signal.

The input section can select one channel from a multiplexed data stream of up to 8 channels. The input enable is delayed by 0 to 7 clock cycles to enable a selection register. The register following the selection register is enabled by the non-delayed input enable to realign the processing of the channels. The one-clock-wide input enable must align with the data for the first channel. The desired channel is then selected by programming the delay. A delay of zero selects the first channel, a delay of 1 selects the second, etc.

The parallel input busses are 16 bits wide. The input format may be twos complement or offset binary format. A floating point mode is also supported. The floating point modes and the mapping of the parallel 16-bit input format is discussed below.

# Floating Point Input Mode Bit Mapping

The input bit weighting for fixed point inputs on busses A, B, C, and D is:

# Floating Point Input Mode Bit Mapping Tables A(15:0), B(15:0), C(15:0) or D(15:0):

bit 15 (MSB):  $2^{0}$ , bit 14:  $2^{-1}$ , bit 13:  $2^{-2}$ , ..., bit 0:  $2^{-15}$ .

For floating point modes, the least significant 2 or 3 bits are used as exponent bits (See Floating Point Input Mode Bit Mapping Tables). The difference between the four floating point modes with three exponent bits is where the exponent saturates.

| 15             | 14              | 13              | 12              | 11              | 10              | 9               | 8               | 7               | 6               | 5                | 4                | 3                | 2                        | 1      | 0      |

|----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|------------------|--------------------------|--------|--------|

| 2 <sup>0</sup> | 2 <sup>-1</sup> | 2 <sup>-2</sup> | 2 <sup>-3</sup> | 2 <sup>-4</sup> | 2 <sup>-5</sup> | 2 <sup>-6</sup> | 2 <sup>-7</sup> | 2 <sup>-8</sup> | 2 <sup>-9</sup> | 2 <sup>-10</sup> | 2 <sup>-11</sup> | 2 <sup>-12</sup> | 2 <sup>-13</sup> /(exp2) | (exp1) | (exp0) |

### 11-BIT MODE: 11 to 13-BIT MANTISSA, 3-BIT EXPONENT, 30dB EXPONENT RANGE

| EXPONENT     | GAIN (dB) |     |     |     |     | PIN | BIT WI | EIGHTI | NG TO | 16-BIT | INPU | Г МАР | PING |    |    |    |    |

|--------------|-----------|-----|-----|-----|-----|-----|--------|--------|-------|--------|------|-------|------|----|----|----|----|

| 000          | 0         | X15 | X15 | X15 | X15 | X15 | X15    | X14    | X13   | X12    | X11  | X10   | X9   | X8 | X7 | X6 | X5 |

| 001          | 6         | X15 | X15 | X15 | X15 | X15 | X14    | X13    | X12   | X11    | X10  | X9    | X8   | X7 | X6 | X5 | X4 |

| 010          | 12        | X15 | X15 | X15 | X15 | X14 | X13    | X12    | X11   | X10    | X9   | X8    | X7   | X6 | X5 | X4 | Х3 |

| 011          | 18        | X15 | X15 | X15 | X14 | X13 | X12    | X11    | X10   | X9     | X8   | X7    | X6   | X5 | X4 | Х3 | 0  |

| 100          | 24        | X15 | X15 | X14 | X13 | X12 | X11    | X10    | X9    | X8     | X7   | X6    | X5   | X4 | Х3 | 0  | 0  |

| 101 (Note 1) | 30        | X15 | X14 | X13 | X12 | X11 | X10    | X9     | X8    | X7     | X6   | X5    | X4   | Х3 | 0  | 0  | 0  |

NOTES:

1. Or 110 or 111, the exponent input saturates at 10.

2. "Xnn" = input A, B, C, or D bit nn.

## 12-BIT MODE: 12 to 13-BIT MANTISSA, 3-BIT EXPONENT, 24dB EXPONENT RANGE

| EXPONENT     | GAIN (dB) |     |     |     | l   | PIN BIT | WEIGH | ITING T | О 16-В | IT INPU | IT MAP | PING |    |    |    |    |    |

|--------------|-----------|-----|-----|-----|-----|---------|-------|---------|--------|---------|--------|------|----|----|----|----|----|

| 000          | 0         | X15 | X15 | X15 | X15 | X15     | X14   | X13     | X12    | X11     | X10    | X9   | X8 | X7 | X6 | X5 | X4 |

| 001          | 6         | X15 | X15 | X15 | X15 | X14     | X13   | X12     | X11    | X10     | X9     | X8   | X7 | X6 | X5 | X4 | Х3 |

| 010          | 12        | X15 | X15 | X15 | X14 | X13     | X12   | X11     | X10    | X9      | X8     | X7   | X6 | X5 | X4 | Х3 | 0  |

| 011          | 18        | X15 | X15 | X14 | X13 | X12     | X11   | X10     | X9     | X8      | X7     | X6   | X5 | X4 | Х3 | 0  | 0  |

| 100 (Note 3) | 24        | X15 | X14 | X13 | X12 | X11     | X10   | X9      | X8     | X7      | X6     | X5   | X4 | Х3 | 0  | 0  | 0  |

NOTE:

3. Or 101, 110, or 111, the exponent input saturates at 100.

### 13-BIT MODE: 13-BIT MANTISSA, 3-BIT EXPONENT, 18dB EXPONENT RANGE

| EXPONENT     | GAIN (dB) |     |     |     | P   | IN BIT | WEIGH | TING TO | D 16-BI | T INPU | Г МАР | PING | i  |    |    |    |    |

|--------------|-----------|-----|-----|-----|-----|--------|-------|---------|---------|--------|-------|------|----|----|----|----|----|

| 000          | 0         | X15 | X15 | X15 | X15 | X14    | X13   | X12     | X11     | X10    | X9    | X8   | X7 | X6 | X5 | X4 | Х3 |

| 001          | 6         | X15 | X15 | X15 | X14 | X13    | X12   | X11     | X10     | X9     | X8    | X7   | X6 | X5 | X4 | Х3 | 0  |

| 010          | 12        | X15 | X15 | X14 | X13 | X12    | X11   | X10     | X9      | X8     | X7    | X6   | X5 | X4 | Х3 | 0  | 0  |

| 011 (Note 4) | 18        | X15 | X14 | X13 | X12 | X11    | X10   | X9      | X8      | X7     | X6    | X5   | X4 | Х3 | 0  | 0  | 0  |

NOTE:

4. Or 100, 101, 110, or 111, the exponent input saturates at 011.

8

| EXPONENT    | GAIN (dB) |     |     |     | Р   | IN BIT V | VEIGHT | ING TO | 16-BIT | INPU | T MA | PPINO | •  |    |    |    |    |

|-------------|-----------|-----|-----|-----|-----|----------|--------|--------|--------|------|------|-------|----|----|----|----|----|

| 00          | 0         | X15 | X15 | X15 | X14 | X13      | X12    | X11    | X10    | X9   | X8   | X7    | X6 | X5 | X4 | Х3 | X2 |

| 01          | 6         | X15 | X15 | X14 | X13 | X12      | X11    | X10    | X9     | X8   | X7   | X6    | X5 | X4 | Х3 | X2 | 0  |

| 10 (Note 5) | 12        | X15 | X14 | X13 | X12 | X11      | X10    | X9     | X8     | Х7   | X6   | X5    | X4 | Х3 | X2 | 0  | 0  |

### 14-BIT MODE: 14-BIT MANTISSA, 2-BIT EXPONENT, 12dB EXPONENT RANGE

NOTE:

5. Or 11, the exponent input saturates at 10.

# Level Detector

An input level detector is provided to monitor the signal level on any of the input busses. Which input bus, the input format, and the level detection type are programmable (see Microprocessor Interface section, Table 39, "INPUT LEVEL DETECTOR SOURCE SELECT/FORMAT REGISTER (GWA = F804h)," on page 44, Table 40, "INPUT LEVEL DETECTOR CONFIGURATION REGISTER (GWA = F805h)," on page 45 and Table 41, "INPUT LEVEL DETECTOR START STROBE REGISTER (GWA = F806h)," on page 45). This signal level represents the wideband signal from the A/D and is useful for controlling gain / attenuation blocks ahead of the converter. The supported monitoring modes are: integrated magnitude (like the HSP50214 without the threshold), leaky integration  $(Y_n = X_n \times A + Y_{n-1} \times (1-A))$  where  $A = 1, 2^{-8}, 2^{-12}$ , or  $2^{-16}$ (see GWA = F805h), and peak detection. The measurement interval can be programmed from 2 to 65537 samples (or continuous for the leaky integrator and peak detect cases). The output is 32 bits and is read via the  $\mu$ P interface.

# NCO/Mixer

After the input select/format section, the samples are multiplied by quadrature sine wave samples from the carrier NCO. The NCO has a 32-bit frequency control, providing sub-hertz resolution at the maximum clock rate. The quadrature sinusoids have exceptional purity. The purity of the NCO should not be the determining factor for the receiver dynamic range performance. The phase quantization to the sine/cosine generator is 24 bits and the amplitude quantization is 19 bits.

The carrier NCO center frequency is loaded via the  $\mu$ P bus. The center frequency control is double buffered - the input is loaded into a center frequency holding register via the  $\mu$ P interface. The data is then transferred from the holding register to the active register by a write to a address IWA \*006h or by a SYNCI signal, if loading via SYNCI is enabled. To synchronize multiple channels, the carrier NCO phase accumulator feedback can be zeroed on loading to restart all of the NCOs at the same phase. A serial offset frequency input is also available for each channel through the D(15:0) parallel data input bus (if that bus is not needed for data input). This is legacy support for HSP50210 type tracking signals. See IWA=\*000 and \*004 for carrier offset frequency parameters.

9

After the mixers, a PN (pseudonoise) signal can be added to the data. This feature is provided for test and to digitally reduce the input sensitivity and adjust the receiver range (sensitivity). The effect is the same as increasing the noise figure of the receiver, reducing its sensitivity and overall dynamic range. For testing, the PN generator provides a wideband signal which may be used to verify the frequency response of a filter. The one bit PN data is scaled by a 16-bit programmable scale factor. The overall range for the PN is 0 to 1/4 full scale (see IWA = \*001h). A gain of 0 disables the PN input. The PN value is formed as

# PN Value

|   |   |   | 2 <sup>-3</sup> | 2 <sup>-4</sup> | • | • | • | • | • | • | • | • | • | • | • | • | 2 <sup>-17</sup> | 2 <sup>-18</sup> |

|---|---|---|-----------------|-----------------|---|---|---|---|---|---|---|---|---|---|---|---|------------------|------------------|

| s | s | s | Х               | Х               | х | х | х | х | х | х | х | х | х | х | х | х | Х                | х                |

where S is the PN generator output bit (treated as a sign bit) and the 16 X's refer to the PN Gain Register IWA = \*001h.

The minimum, non-zero, PN value is  $2^{-18}$  of full scale (-108dBFS) on each axis (-105dBFS total). For an input noise level of -75dBFS, this allows the SNR to be decreased in steps of 1/8dB or less. The I and Q PN codes are offset in time to decorrelate them. The PN code is selected and enabled in the test control register (F800h). The PN is added to the signal after the mix with the three sign bits aligned with the most significant three bits of the signal, so the maximum level is -12dBFS and the minimum, non-zero level is -108dBFS. The PN code can be  $2^{15}$ -1,  $2^{23}$ -1 or  $2^{15}$ -1 \*  $2^{23}$ -1.

# **CIC** Filter

Next, the signal is filtered by a cascaded integrator/comb (CIC) filter. A CIC filter is an efficient architecture for decimation filtering. The power or magnitude squared frequency response of the CIC filter is given by:

$$\mathsf{P}(f) = \left(\frac{\sin(\pi M f)}{\sin\left(\frac{\pi f}{R}\right)}\right)^{2\mathsf{N}}$$

where

M = Number of delays (1 for the HSP50216)

N = Number of stages

and R = Decimation factor.

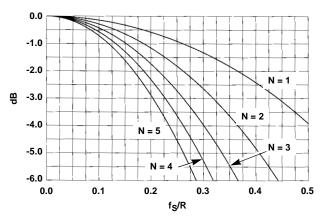

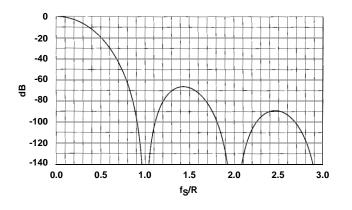

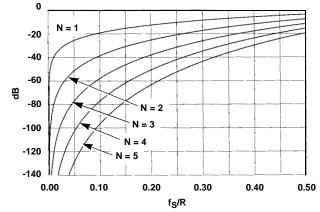

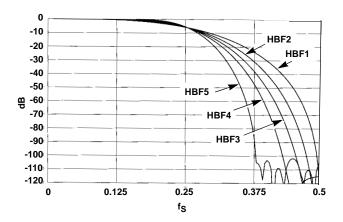

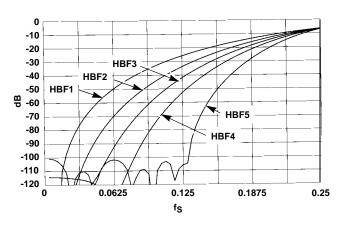

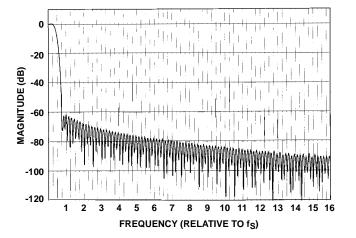

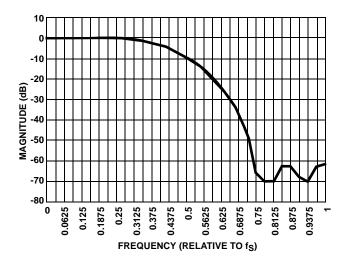

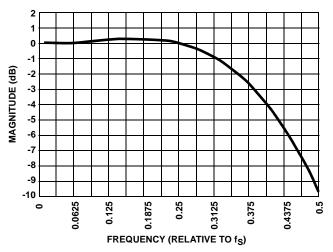

The passband frequency response for 1<sup>st</sup> (N=1) though 5<sup>th</sup> (N=5) order CIC filters is plotted in Figure 8. The frequency axis is normalized to  $f_S/R$ , making  $f_S/R = 1$  the CIC output sample rate. Figure 10 shows the frequency response for a 5<sup>th</sup> order filter but extends the frequency axis to  $f_S/R = 3$  (3 times the CIC output sample rate) to show alias rejection for the out of band signals. Figure 9 uses information from Figure 10 to provide the amplitude of the first (strongest) alias as a function of the signal frequency or bandwidth from DC. For example, with a 5<sup>th</sup> order CIC and  $f_S/R = 0.125$  (signal frequency is 1/8 the CIC output rate) Figure 9 shows a first alias level of about -87 dB. Figure 9 is also listed in table form in Table 47.

The CIC filter order is programmable from 0 to 5. The minimum decimation is 4. If the order is set to 0, there must be at least 4 clocks between samples or the decimation counter must be set to 4 to chose every 4th sample.

The integrator bit widths are 69, 62, 53, 44, and 34 for the 1<sup>st</sup> through 5<sup>th</sup> stages, respectively, while the comb bit widths are all 32. The integrators are sized for decimation factors of up to 512 with 5 stages, 2048 with 4 stages, 32768 with 3 stages, and 65536 with 1 or 2 stages. Higher decimations in the CIC should be avoided as they will cause integrator overflow. In the HSP50216, the integrators are slightly oversized to reduce the quantization noise at each stage.

# **Backend Data Routing**

A CIC filter has a gain of  $\mathbb{R}^{N}$ , where R is the decimation factor and N is the number of stages. Because the CIC filter gain can become very large with decimation, an attenuator is provided ahead of the CIC to prevent overflow. The 24 bits of sample data are placed on the low 24 bits of a 69 bit bus (width of the first CIC integrator) for a gain of  $2^{-45}$ . A 32 bit barrel shifter then provides a gain of  $2^{0}$  to  $2^{31}$  inclusive before passing the data onto the CIC. The overall gain in the pre-CIC attenuator can therefore be programmed to be any one of 32 values from  $2^{-45}$  to  $2^{-14}$ , inclusive (see IWA=\*004, bits 18:14). This shift factor is adjusted to keep the total barrel shifter and CIC filter between 0.5 and 1.0. The equation which should be used to compute the necessary shift factor is:

Shift Factor =  $45 - \text{Ceiling}(\log_2(\mathbb{R}^N))$ .

NOTE: With a CIC order of zero, the CIC shifter does not have sufficient range to route more than 10 bits to the back end since the maximum gain is  $2^{-14}$  (the least significant 14 bits are lost).

# **Back End Section**

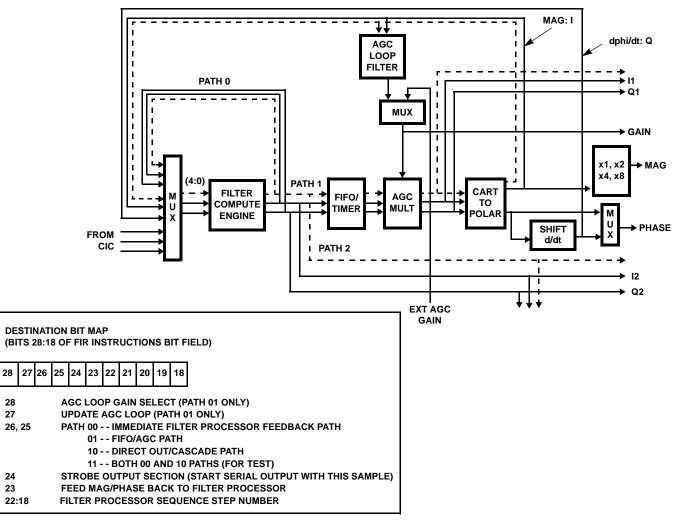

One back-end processing section is provided per channel. Each back end section consists of a filter compute engine, a FIFO/timer for evenly spacing samples (important when implementing interpolation filters and resamplers), an AGC and a cartesian-to-polar coordinate conversion block. A block diagram showing the major functional blocks and data routing is shown above. The data input to the back end section is through the filter compute engine. There are two other inputs to the filter compute engine, they are a data recirculation path for cascading filters and a magnitude and  $d\phi/dt$  feedback path for AM and FM filtering. There are seven outputs from each back end processing section. These are I and Q directly out of the filter compute engine (I2, Q2), I and Q passed through the FIFO and AGC multipliers (I1, Q1), magnitude (MAG), phase (or  $d\phi/dt$ ), and the AGC gain control value (GAIN). The I2/Q2 outputs are used when cascading back end stages. The routing of signals within the back end processing section is controlled by the filter compute engine. The routing information is embedded in the instruction bit fields used to define the digital filter being implemented in the filter compute engine.

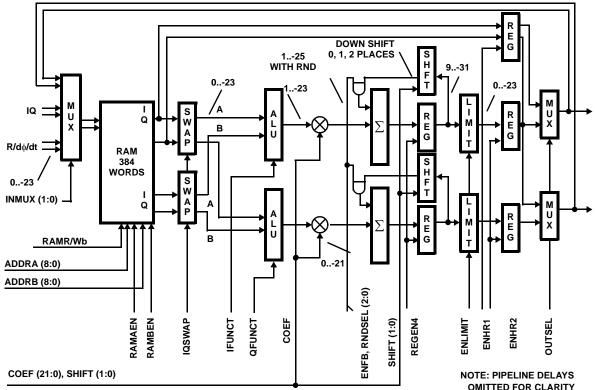

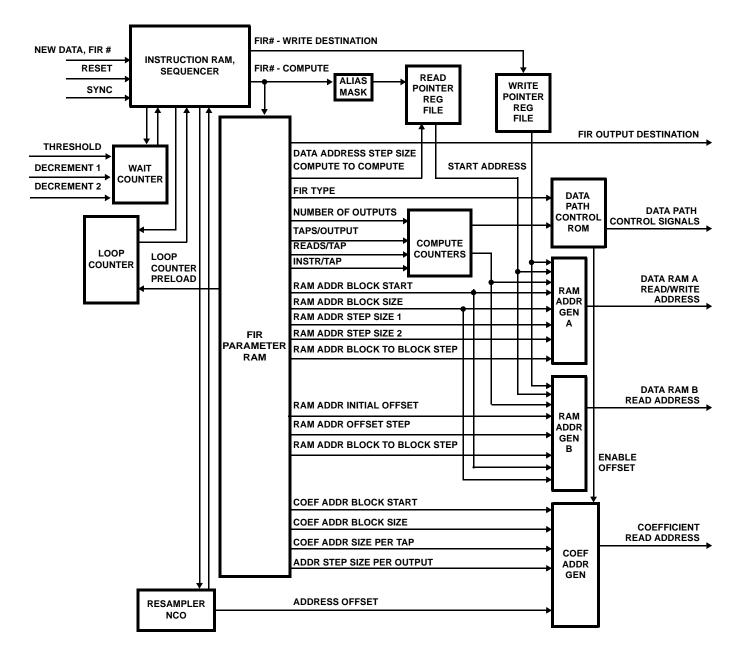

# Filter Compute Engine

The filter compute engine is a dual multiply-accumulator (MAC) data path with a microcoded FIR sequencer. The filter compute engine can implement a single FIR or a set of filters. For example, the filter chain could include two halfband filters, a shaping (matched) filter and a resampling filter, all with different decimations. The following filter types are currently supported by the architecture and microcode:

- Even symmetric with even # of taps decimation filters

- Even symmetric with odd # of taps decimation filters (including HBFs)

- · Odd symmetric with even # of taps decimation filters

- Odd symmetric with odd # of taps decimation filters

- Asymmetric decimation filters •

- Complex filters

- Interpolation filters (up to interpolate by 4)

- ٠ Interpolation halfband filters

- Resampling filters (under resampler NCO control) •

- Fixed resampling ratio filter (within the available number of • coefficients)

- Quadrature to real filtering (w/ fs/4 up conversion)

The input to the filter compute engine comes from one of three sources - a CIC filter output (which can also be another backend section), the output of the filter compute engine (fed back to the input) or the magnitude and do/dt fed back from the cartesian-to-polar coordinate converter.

**OMITTED FOR CLARITY**

The number and size of the filters in the chain is limited by the number of clock cycles available (determined by the decimation) and by the data and coefficient RAM/ROM resources. The data RAM is 384 words (I/Q pairs) deep. The data addressing is modulo in power-of-2 blocks, so the maximum filter size is 256. The block size and the block starting memory address for each filter is programmable so that the available memory can be used efficiently. The coefficient RAM is 192 words deep. It is half the size of the data memory because filter coefficients are typically symmetric. ROMs are provided with halfband filter coefficients, resampling filter coefficients, and constants. The filter compute engine exploits symmetry where possible so that each MAC can compute two filter taps per clock, by doing a pre-add before multiplying. In the case of halfband filters, the zero-valued coefficients are skipped for extra efficiency. There is an overhead of one clock cycle per input sample for each filter in the chain (for writing the data into the data RAM) and (except in special cases) a two clock cycle overhead for the entire chain for program flow control instructions.

The output of the filter compute engine is routed through a FIFO in the main output path. The FIFO is provided to more evenly space the FIR outputs when they are produced in bursts (as when computing resampling or interpolation filters). The FIFO is four samples deep. The FIFO is loaded by the output of the filter when that path is selected. It is unloaded by a counter. The spacing of the output samples is specified in clock periods. The spacing can be set from 1 (fall through) to 4096 samples

(approximately the spacing for a 16KSPS output sample rate when using 65MSPS clock) using IWA = \*00Ah bits 11:0.

The number and order of the filtering in the filter chain is defined by a FIR control program. The FIR control program is a sequence of up to 32 instruction words. Each instruction word can be a filter or program flow instruction. The filter instruction defines a FIR in the chain, specifying the type of FIR, number of taps, decimation, memory allocation, etc. For program flow, a wait for input sample(s) instruction, a loop counter load, and several jumps (conditional and unconditional) are provided. The HSP50216 evaluation board includes software for automatically generating FIR control programs for most filter requirements. Examples of programs FIR control programs are given below.

The simplest filter program computes a single filter. It has three instructions (see Sample Filter #1 Program Instructions below):

### SAMPLE FILTER #1 PROGRAM

| STEP | INSTRUCTION                                                                                                                                                                                                                     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | Wait for enough input samples (equal to the decimation factor)                                                                                                                                                                  |

| 1    | FIR<br>Type = even symmetric<br>95 taps<br>Decimate by 2<br>Compute one output<br>Decrement wait counter<br>Memory block size 128<br>Memory block start at 64,<br>Coefficient block start at 64<br>Step size 1<br>Output to AGC |

| 2    | Jump, Unconditional, to step 0                                                                                                                                                                                                  |

The parameters of the FIR (including type, number of taps, decimation and memory usage) are specified in the bit fields of the step 1 instruction word. To change the filtering the only other change needed is the number of samples in the wait threshold register (IWA = \*00C, bits 9:0). The filter in this example requires 52 clock cycles to compute, allocated as follows:

| CLOCK<br>CYCLES | FUNCTION PERFORMED                                                                                |

|-----------------|---------------------------------------------------------------------------------------------------|

| 48              | Clocks for FIR computation (two taps/clock due to symmetry)                                       |

| 2               | Clocks for writing the input data into the data RAMs (Decimate by 2 requires 2 inputs per output) |

| 2               | Clocks for the program flow instructions (wait and jump)                                          |

| 52              | Total                                                                                             |

Using a 65MSPS clock, the output sample rate could be as high as 65MSPS / 52 clocks = 1.25MSPS. The input sample

rate to the FIR from the CIC filter would be 2.5MSPS. The impulse response length would be 38  $\mu$ sec (95 taps at 0.4 $\mu$ s/tap).

Each additional filter added to the signal processing chain requires one instruction step. As an example of this, a typical filter chain might consist of two decimate-by-2 halfband filters being followed by a shaping filter with the final filter being a resampling filter. The program for this case might be (see Sample Filter Program #2 Program Instructions below):

| SAMPL | E FILT | ER #2 | PROGRAM |

|-------|--------|-------|---------|

|-------|--------|-------|---------|

| STEP | INSTRUCTION                                                                                                                                                                                                                 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | Wait for enough input samples (usually equal to the total decimation 8 in this case)                                                                                                                                        |

| 1    | FIR<br>Type = even symmetry<br>15 taps<br>Halfband<br>Decimate by 2<br>Compute four outputs<br>Memory block size 32<br>Memory block start at 0<br>Coefficient block start at 13<br>Output to step 2<br>Decrement wait count |

| 2    | FIR<br>Type = even symmetry<br>23 taps<br>Halfband<br>Decimate by 2<br>Compute two outputs<br>Memory block size 32<br>Memory block start at 32<br>Coefficient block start at 24<br>Output to step 3                         |

| 3    | FIR<br>Type = even symmetry<br>95 taps<br>Decimate by 2<br>Compute one output<br>Memory block size 128<br>Memory block start at 64<br>Coefficient block start at 64<br>Step size 1<br>Output to step 4                      |

| 4    | FIR<br>Type = resampler<br>Increment NCO<br>6 taps<br>Compute one output<br>Memory block size 8<br>Memory block starts at 192<br>Coefficient block start at 512<br>Step size 32<br>Output to AGC                            |

| 5    | Jump, Unconditional, to 0                                                                                                                                                                                                   |

Sample filter #2 requires:

- 32 + 32 + 128 + 8 = 200 data RAM locations

- (95+1)/2=48 coefficient RAM location (resampler and HBF coefficients are in ROM).

The number of clock cycles required to compute an output for Sample filter #2 is calculated as follows:

## SAMPLE FILTER #2 CLOCK CYCLES CALCULATION

| CLOCK<br>CYCLES | FUNCTION PERFORMED                                        |

|-----------------|-----------------------------------------------------------|

| 20              | Halfband 1 compute clocks<br>(5 per compute x 4 computes) |

| 8               | Halfband 1 input sample writes (8 input samples)          |

| 14              | Halfband 2 compute clocks<br>(7 per compute x 2 computes) |

| 4               | Halfband 2 input sample writes (4 input samples)          |

| 48              | 95 tap symmetric FIR, 2 clocks per tap                    |

| 2               | FIR input sample writes (2 input samples)                 |

| 6               | resampler (6 taps, nonsymmetric)                          |

| 1               | Resampler input sample write (1 input samples)            |

| 1               | Jump instruction                                          |

| 1               | Wait instruction                                          |

| 105             | Clock cycles per output                                   |

Total decimation is 8, so the input sample rate for the FIR chain (CIC output rate) could be up to:

$f_{CLK}/(ceil(105/8)) = f_{CLK}/14.$

With a 65MHz clock, this would support a maximum input sample rate to the FIR processor of 4.6MHz and an output sample rate up to 0.580MHz. The shaping filter impulse response length would be:

(95 x 2)/580,000 = 82µs.

The maximum output sample rate is dependent on the length and number of FIRs and their decimation factors.

Illustrating this concept with Filter Example #3, a higher speed filter chain might be comprised of one 19 tap decimate-by-2 halfband filter followed by a 30 tap shaping FIR filter with no decimation. The program for this example could be:

## SAMPLE FILTER #3 PROGRAM

| STEP | INSTRUCTION                                    |

|------|------------------------------------------------|

| 0    | Wait for enough input samples (2 in this case) |

### SAMPLE FILTER #3 PROGRAM (Continued)

| STEP | INSTRUCTION                                                                                                                                                                                                           |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | FIR<br>Type = even symmetry<br>19 taps<br>Halfband<br>Decimate by 2<br>Compute one output<br>Memory block size 32<br>Memory block start at 0<br>Coefficient block start at 18<br>Output to step 2<br>Reset wait count |

| 2    | FIR<br>Type = even symmetry<br>30 taps<br>Decimate by 1<br>Compute one output<br>Memory block size 64<br>Memory block start at 32<br>Coefficient block start at 64<br>Step size 1<br>Output to AGC                    |

| 3    | Jump, Unconditional, to 0                                                                                                                                                                                             |

The number of clock cycles required to compute an output for Sample filter #3 is calculated as follows:

# SAMPLE FILTER #3 CLOCK CYCLES CALCULATION

| CLOCK<br>CYCLES | FUNCTION PERFORMED                      |

|-----------------|-----------------------------------------|

| 6               | 19 tap halfband, one output             |

| 2               | halfband input writes (2 input samples) |

| 15              | 30 tap symmetric FIR, 2 taps per clock  |

| 1               | 1 FIR input write                       |

| 1               | 1 wait                                  |

| 1               | 1 jump                                  |

| 26              | Clock cycles per output                 |

For Filter Example #3 and a 65MSPS input, the maximum FIR input rate would be 65MSPS / ceil(26 / 2) = 5MSPS giving a decimate-by-2 output sample rate of 2.5MSPS. At 70MSPS, the FIR could have up to 34 taps with the same output rate.

Channels 0, 1, 2 and 3 can be combined in a polyphase structure for increased bandwidth or improved filtering.

Filter Example #4 will be used to demonstrate this capability.

Symbol rate of 4.096 MSym. The desired output sample rate is 8.192MSPS. Arrange the four back end sections as four filters operating on the same CIC output at a rate of

65.536MHz/4=16.384MHz, where the factor of 4 is the CIC decimation we have chosen.

Each channel computes the same sequence, offset by one output sample from the previous sample (see IWA = \*00Bh). Each channel decimates down to 2.048M and then the

channels are multiplexed together in the output formatter to get the desired 8.192MSPS. The input sample rate to the final filter of each channel must meet Nyquist requirements for the final output to assure that no information is lost due to aliasing.

### SAMPLE FILTER #4 PROGRAM

| STEP | INSTRUCTION                                                                                                                                                                                                                                       |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | Wait for enough input samples (8 in this case)                                                                                                                                                                                                    |

| 1    | FIR<br>type = even symmetry<br>44 taps<br>decimate by 8<br>compute one output<br>memory block size 64<br>memory block start at 0<br>coefficient block start at 64<br>step size 1<br>output to AGC<br>offset memory read pointers by 0, -2, -4, -6 |

| 2    | Jump, Unconditional, to 0                                                                                                                                                                                                                         |

The number of FIR taps available for these requirements is calculated as follows:

65536/2048 = 32 clocks

minus (8 writes + 1 wait + 1 jump = 10 clocks)

= 22 clocks

Therefore, the number of taps available is:

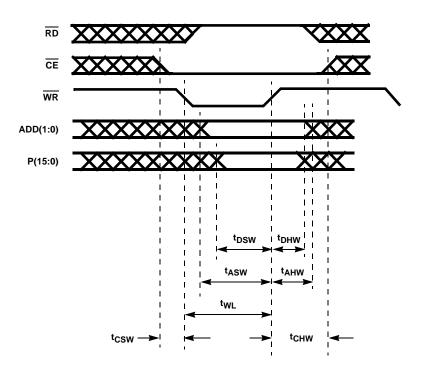

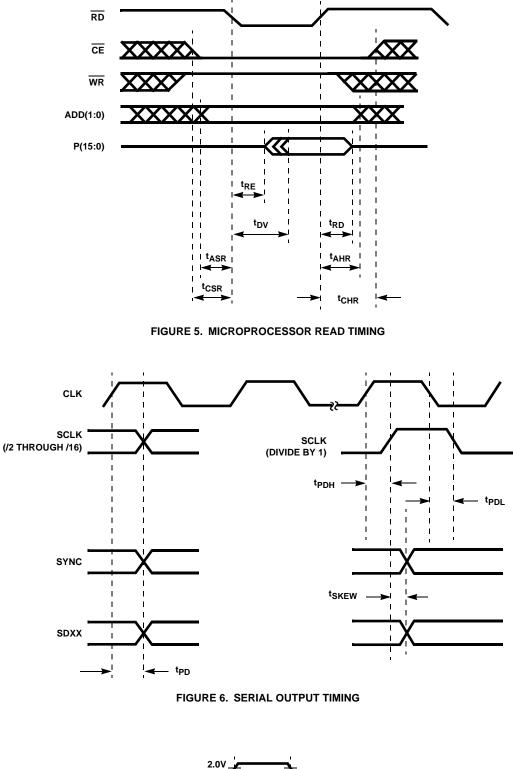

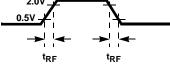

22 x 2 = 44 taps.